基于HWD32F429的主从冗余数据记录系统的设计

作者: 陈润星 刘杰 李龙杰 何鹏赓 李泽银 石义金

关键词:HWD32F429;数据记录;Modbus协议;eMMC存储

0 引言

目前国内多数嵌入式的数据记录系统常用STM32 系列作为主控MCU,以国产MCU设计的数据记录系统较少,针对这一问题设计了一款基于国产MCU的主从冗余数据记录系统,可实现双通道Modbus协议数据的存储和读取,该系统高效稳定,可在多种需要数据存储场景进行使用。基于HWD32F429的主从冗余数据记录系统,以国产HWD32F429替代STM32系列的芯片,可以使整个系统的全国产化率超过98%。

1 数据记录系统的硬件设计

1.1 HWD32F429芯片

HWD32F429 系列是基于 ARM® Cortex®-M4 32-bit RISC CPU,最高工作频率 240MHz 的高性能MCU。HWD32F429 集成了丰富的外设接口,包括 SPI、I2C、UART、CAN、网口等,适用于多种应用场景,如工业控制、智能家居、物联网等。

HWD32F429 系列提供 144pin、176pin 的 LQFP 封装,208pin 的 TFBGA 封装,用于高性能变频控制、数字电源、智能硬件、IoT 连接模块等领域。此外,该芯片还具有错误处理和诊断功能,可以实现故障检测和定位,提高了系统的可靠性和稳定性。

本文设计数据记录系统主控HWD32F429采用144pin的LQFP 封装。

1.2 数据接收模块

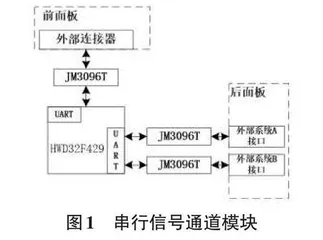

基于国产芯片HWD32F429数据记录系统与外部接口模块间有3路串行通信接口,其中2路接收来自外部系统A、B的待存储数据并互为冗余[1],另外1路串行通信作对外调试接口,用于接收上位机发送的调试命令,串行通道设计示意图如图1所示。

数据接收均通过UART+JM3096T 收发器实现,JM3096T是一款国产高可靠性隔离全双工RS422收发器,实现控制信号与现场信号的隔离及电平转换。其中一路接收模块原理图如图2所示。

1.3 eMMC 存储模块

高速eMMC 存储芯片TEE12833TW0 具有高集成、高性能、低功耗以及高数据吞吐量等特点,其单片存储容量可达128GB,本身内部集成控制芯片可以自我管理坏块以及错误检测和纠正,该国产eMMC存储芯片采用标准接口可被广泛应用在通信、军事、航天、航空等领域的数据采集与存储系统。数据记录系统存储模块原理图如图3所示。

1.4 以太网通信模块

数据记录系统有一路以太网通信接口作为上位机读取数据的接口。接口设置在前面板,方便操作员连接。以太网通信模块设计如图4所示。

HWD32F429 自带MAC 功能,并提供MII 接口。PHY芯片采用EM971AP型芯片。EM971AP为一款支持10/100 兆的以太网物理收发器电路,集成以太网PHY,支持10BASE-T、100BASE-TX,支持MII 接口,能够替换LXT971A芯片。网络变压器采用LT1306-A,实现对外的10/100Mbps自适应以太网通信功能,以太网通信原理图设计见图5所示。

2 数据记录系统软件设计

2.1 软件设计架构

数据记录系统嵌入式软件主要4个功能任务:数据接收任务、数据存储任务、数据读取任务、错误处理任务。软件体系架构如图6所示。这些任务模块利用FreeRTOS的多任务并行处理技术,通过消息和信号量的同步机制实现彼此的同步协作。

在数据记录系统启动成功后,系统首先通过初始化模块来确保硬件的正确启动。接着,系统会开启功能调度任务,创建一个消息指针队列,用于管理进程的开启,并监控数据通信的状态。

数据接收任务通过两路 UART 接收来自外部系统的数据,为了确保系统的可靠性,采用 Modbus 通信协议进行数据传输。数据存储任务负责将UART 接收到的数据存储到 eMMC 存储芯片中。数据读取任务则通过以太网口等待数据读取查询指令,一旦检测到查询指令,就读取 eMMC 相应数据。通常情况下,数据记录系统的数据读取过程都在非工作状态下进行,因此当系统进入数据读取任务时,会关闭其他任务,以保证读取操作的独立性。为了提高开发效率和可靠性,软件移植了FATFS 和 LwIP,分别用于辅助完成文件管理和网络处理[2-5]。

系统功能调度任务负责启动其他功能任务。在初次运行时,它将开启数据接收任务。

2.2 数据接收任务

数据记录系统通过两路UART接收从外部系统传入的数据,两路数据接收通道互为冗余,系统连接图如图7所示。

为了保证数据的可靠性,采用Modbus通信协议,数据记录系统作为从机,外部待存储设备作为主机,配置设备地址0xe7,功能码为16,对应为写入多点数据,由于Modbus 协议规定单帧数据大小不超过256Bytes,所以当待存储数据超过256Bytes,需要被分为多帧Modbus数据,接收到多帧数据后再组帧形成待存储的数据,存储数据请求帧格式示意图如图8 所示。

当数据存储系统接收到串口中断数据,则对接收数据按照Modbus协议进行解帧和校验处理,根据校验结果返回响应数据,用于通知主机Modbus数据帧是否接收成功。返回的响应数据如图9所示。

考虑到系统运行过程中数据接收时间可能具有随机性,为确保系统高效运行,我们建立了一个深度为 256 的 FIFO,用于暂存已接收到的数据,防止存储数据和接收数据发生冲突,导致数据丢失。只有在数据验证无误时,才会启动相关的数据存储进程,从而实现多任务双工。

2.3 数据存储任务

数据存储任务是整个系统的关键所在,解决数据可靠高效地写入进eMMC存储芯片的问题。FreeR⁃TOS的内核未带文件系统,为了简化编程流程以及提升开发效率,在设计中加入高效、资源占用率低、专为小型嵌入式系统设计的文件管理系统FATFS。

为了方便对数据存储和读取时的查找,数据文件以每帧数据开头的时间戳配合其他信息命名。文件名参数对应关系如图所示,其中NO用于区分一秒内多帧存储数据的次序数,通道号用于区分两路存入数据的UART通道,确保每一帧数据都能被正确保存且可以区分。

2.4 数据读取任务

数据记录系统另一个关键功能是确保存储在eMMC中的数据能够快速准确地读取出来。针对大容量存储的情况下,快速查找并及时返回某个文件对操作员使用体验来讲有重要的意义。本文的数据记录系统采用以太网作为数据读取的传输途径。利用第三方LwIP网络协议栈实现网络通讯功能。当接收到来自以太网的数据读取指令,首先检查指令合法性,如果查询指令合法,则向任务管理进程发送网络查询数据接收成功消息。

2.5 错误处理任务

从系统安全角度出发,最理想的错误处理策略是尽量规避错误。当无法避免或纠正错误时,应采取相应的报警措施。此外,系统应根据错误的严重程度对错误进行分类。本软件依据对系统功能影响程度对错误进行分级处理,分类标准与分类结果如图11 所示。

存储芯片中应建立一个专门用于记录系统错误的日志文件,以记录发生的所有错误。当发生第 III 类低风险错误时,黄色指示灯应常亮;当发生II 类中风险错误时,橙色指示灯闪烁;当发生第 I 类高风险错误时,红色指示灯应始终闪烁,直到操作员排除故障且系统重新上电。发生风险错误可通过调试串口实时输出,错误类型,方便操作员排除故障。

3 系统测试

为了验证基于HWD32F429数据记录系统的功能和性能,采用QT软件平台设计了数据记录系统测试软件,用于模拟数据的存储、读取以及校验功能。系统测试连接示意图如图12所示。

该测试软件间隔50ms 发送数据长度为256 的Modbus协议帧,通过连接网络读取校验双通道存储的数据,测试软件如图13所示。

4 结束语

本文设计的主从冗余数据记录系统主要采用ARM+eMMC 的架构,选用国产芯片 HWD32F429 作为主控制器。该系统能够满足以 Modbus 为协议的各类设备的数据记录需求,在实现嵌入式设备的国产化替代方面具有一定的价值。