利用Logism和头歌重构计算机组成原理实验教学

作者: 熊太平 陈宏 管军霖

关键词:Logisim;头歌;虚拟仿真;计算机组成原理;实验教学

中图分类号:G642 文献标识码:A

文章编号:1009-3044(2024)18-0156-04

0 引言

计算机组成原理的实验方式通常有两种:传统实验箱方式和FPGA(现场可编程逻辑门阵列)开发板方式。传统实验箱方式基于分离元件来开展实验,具有可靠性低、调试难、验收难、成本高等特点,实验偏验证而轻设计。基于FPGA的实验,则具有学习周期长、技术要求高、指导难、抽象度高等特点,且需要重构课程教学体系,需先修硬件描述语言编程方面的课程。目前,教育部要求大学淘汰“水课”、建设“金课”,并提出“两性一度”的金课标准,实验箱方式因其重验证而轻设计的属性逐渐被淘汰。基于FPGA的实验方式,能较好地满足高阶性、创新性和挑战度方面的要求,因而被很多大学所采用,但其对先修课程、学生技术能力以及实验学时的高要求,也限制了它的实际教学效果以及更广泛的应用[1-2]。

目前,计算机大类中的软件工程、信息安全等专业,大多没有开设电路分析、模拟电子、硬件描述语言等硬件类课程,若基于FPGA来开设计算机组成原理实验,对于这些专业的学生来说,要完成设计性的实验项目,难度过大,难以在规定的实验学时下顺利完成。本课程要求学生掌握计算机硬件系统主要组成部件的工作原理和设计方法,具备对相关硬件系统进行分析和设计的能力,若不能顺利完成设计性的实验任务,这些教学目标将无法达成。为适应这种现实状况,并且不降低课程的教学目标要求,一种可行的方案是采用虚拟仿真平台Logisim,并结合头歌实践教学平台(Edu⁃Coder) 来开展实验。Logisim虚拟仿真平台具有以下特点:1) 简单易学、易于调试、零实验成本、无场地和人员要求;2) 支持子电路封装,易于构建复杂数字电路系统,比如CPU;3) 延续了数字逻辑课程中数字电路的设计方法,回避了硬件描述语言过于抽象以及硬件设计程序化的问题,有利于培养学生的硬件设计思维[3]。头歌实践教学平台涵盖了计算机、大数据、云计算、人工智能、软件工程、物联网等专业课程,是学、练、评、测一体化的线上实验环境,有利于学生充分利用课余时间进行实验,延展学生的实际实验课时[4-5]。

1 Logisim 虚拟仿真平台

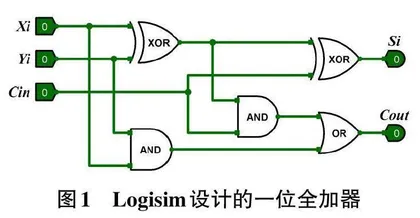

Logisim是一款用于数字电路设计和仿真的开源软件,拥有直观的图形用户界面,允许用户通过拖放元件来设计数字电路。这种图形界面使得电路设计变得更加可视化和易于理解。Logisim包含了大量常用的数字电路元件,如逻辑门、触发器、寄存器等。Logisim拥有非常好的数字电路仿真功能,使用户可以方便、高效地模拟电路的工作过程,观察信号的传递和状态的变化,从而验证电路的正确性。Logisim还提供了良好的调试功能,包括单步执行和断点设置,以便用户能够逐步检查电路的运行过程,找出潜在的问题和错误。Logisim支持层次化设计,允许用户将一些复杂的电路模块化,从而更好地组织和管理大型电路设计[6-8]。图1是用Logisim设计的一位全加器。

2 教改前的实验内容

2.1 实验1:Max+plusⅡ开发系统的使用

实验目的:熟悉Max+plusⅡ系统工作环境;熟悉Max+plusⅡ开发流程;掌握VHDL源程序的基本结构及编程方法;了解硬件设计的规范和流程。

实验内容:PC、LS273、ROM等功能模块的源程序文件以及工程顶层文件的创建、编译和仿真。

2.2 实验2:直接补码阵列乘法器设计

实验目的:掌握直接补码阵列乘法器的组成和工作原理;掌握0类全加器、1类全加器、2类全加器的设计方法;掌握直接补码阵列乘法器的设计和仿真方法。

实验内容:加器设计,n×n位直接补码阵列乘法器设计,直接补码阵列乘法器的仿真测试。

2.3 实验3:SRAM 存储器设计

实验目的:掌握静态随机存储器SRAM的工作特性及其数据的读写方法。

实验内容:时序产生器设计,程序计数器设计,地址寄存器设计,SRAM系统设计,顶层电路设计。

2.4 实验4:指令系统与微程序设计

实验目的:掌握指令格式的设计方法;掌握汇编语言程序的设计方法;熟悉汇编语言程序与机器语言程序之间的转换;掌握微程序流程图的设计方法和微指令代码的设计方法。

实验内容:模型机指令格式和指令系统设计,模型机机器语言程序及相应的汇编语言程序的设计,指令的微程序流程图设计,微指令格式及微程序设计,微程序控制器中地址转移电路的逻辑表达式设计,顶层电路设计。

3 教改后的实验内容

3.1 实验1:32位ALU设计

实验目的包括:掌握算术逻辑运算单元(ALU) 的基本构成;掌握Logisim中各种运算组件的使用方法,熟悉多路选择器的使用;掌握ALU 的设计和仿真方法。

实验内容分为两部分,必做内容和选做内容。必做内容是快速加法器设计和算术逻辑单元(ALU) 设计,具体包括6关:8位可控加减法器设计、4位可级联先行进位电路设计、4位快速加法器设计、16位快速加法器设计、32位快速加法器设计和32位ALU设计。选做内容是乘法器设计,具体包括5关:5位阵列乘法器设计、6位补码阵列乘法器设计、五位流水线乘法器设计、原码一位乘法器设计和补码一位乘法器设计。

本实验的核心任务是设计32位ALU,具体步骤是:1) 设计4位可级联先行进位电路;2) 利用4位可级联先行进位电路来设计4位快速加法器;3) 利用前面两步得到的电路,通过添加合适的连线得到16位和32位快速加法器;4) 利用得到的32位快速加法器,加上移位器、多路选择器、比较器以及逻辑门(与、或、非、异或)等系统固有器件,设计出最终的32位ALU。

32位ALU的输入信号包括:32位操作数X、32位操作数Y、4位操作码ALU_OP;输出信号包括:32位输出结果Result、32位输出结果Result2、有符号运算溢出标志OF、无符号运算溢出标志UOF。ALU操作码的编码及其对应功能如表1所示。

本实验必做内容中,ALU要实现乘、除运算,需利用Logisim本身提供的乘法和除法运算器。对于能力强的同学,鼓励他们完成选做内容,设计实现乘法器,甚至是除法器,从而可以在ALU中使用自己设计的乘法和除法运算器。

3.2 实验2:存储系统设计

实验目的包括:掌握主存地址基本概念和存储器扩展基本思想,能构建同时支持字节、半字和字访问的存储子系统;能熟练使用多路选择器、译码器、寄存器等Logisim组件构建MIPS寄存器文件;理解Cache 实现的关键技术。

实验内容分为必做内容和选做内容两部分。必做内容是存储器设计,具体包括3关:汉字字库的存储扩展、MIPS寄存器文件设计和MIPS RAM设计。选做内容是Cache设计,具体包括4关:全相联cache设计、直接相联cache设计、2路组相联Cache设计和4路组相联cache设计。

汉字字库的存储扩展也即是存储系统扩展,包括两个方面。第一,利用字扩展,把四个4K×32 位的ROM芯片,扩展成16K×32位的存储体。第二,利用位扩展,把7个16K×32位的ROM芯片以及上一步得到16K×32位的存储体,扩展成16K×256位的存储体。

MIPS寄存器文件设计实验,要求利用 Logisim 平台构建一个简化的 MIPS 寄存器文件,内部包含4个32位寄存器,其具体引脚与功能描述如表2所示。

MIPS RAM设计实验,要求利用4个8位的 RAM 组件进行扩展,设计完成能按照8位、16位和32位三种方式进行读写访问的32位存储器,存储器引脚定义如表3所示。

本实验中的选做内容是Cache 设计,实验应以Cache的行设计为主体。直接相联的Cache行应包含有效位、标记和数据块三个寄存器。全相联和组相联的Cache行应包含有效位、标记和数据块三个寄存器以及置换计数器。全相联和组相联Cache写入时,优先选择空行,若无空行,则替换计数器值最大的行,设计时要用到优先编码器和归并比较电路。

3.3 实验3:MIPS处理器设计

实验目的:掌握现代时序硬布线控制器和微程序控制器的基本原理和设计方法。

实验内容也分为必做内容和选做内容两部分。必做内容是采用微程序的单总线CPU设计,具体包括5关:MIPS指令译码器设计,单总线CPU微程序入口查找逻辑设计,单总线CPU微程序条件判别测试逻辑设计,单总线CPU微程序控制器设计,采用微程序的单总线CPU的功能测试。选做内容包括2关:现代时序硬布线控制器状态机设计,现代时序硬布线控制器设计。

在用Logisim做实验之前,应该先设计所有指令的执行流程图,包括数据流和控制流,并以时钟周期为单位构建指令执行状态转换图。对于现代时序微程序控制器,一个状态对应一条微指令,状态的编号通常就是该条微指令的控存地址。

MIPS指令译码器设计实验,要求根据指令的OP 位段和funct位段生成相应指令的译码信号,两个位段都为6位。MIPS指令分为R型指令、I型指令和J型指令三种。R型指令,OP位段的值恒为“000000”,需结合funct 位段来译码;另外两种指令,OP 位段不为“000000”且没有funct位段,只需根据OP位段译码。

单总线CPU微程序入口查找逻辑设计实验,要求在“指令译码信号”和“指令对应微程序的首条微指令的控存地址”之间建立联系。可以利用真值表来辅助设计,真值表的输入是译码信号,输出是控存地址。

单总线CPU微程序条件判别测试逻辑设计实验,要求根据微指令字中的判别测试字段和条件反馈信息来生成后续地址的多路选择信号。由于实验所用CPU模型的测试只有两个,指令测试和beq(对应程序状态字的ZF位)测试[9],因此,后续地址有三种可能,分别是微指令的下址字段(对应无测试或测试不成功)、微程序入口查找逻辑电路的输出(对应指令测试)、beq分支地址(对应beq测试且测试成功)。

单总线CPU微程序控制器设计实验分为两步。第一,设计好微指令格式,然后根据前面得到的指令执行流程图和状态转换图设计出各条微指令;第二,把设计好的微程序拷入控存,并把前面设计的程序入口查找逻辑、判别测试逻辑和控存等连接起来。

必做内容最后一关,采用微程序的单总线CPU的功能测试,在RAM中加载一个冒泡排序程序,程序运行结束后,可以在RAM中查看排序结果。

选做内容是现代时序硬布线控制器的设计。对于能力强的同学,鼓励他们完成,从而可以对比两种控制器的优劣。

4 教改前后对比及教改效果

在桂林电子科技大学计算机与信息安全学院,计算机组成原理被列入软件工程、信息安全等专业的学科基础必修课程。课程以讲授数字计算机系统及其主要组成部件的工作原理为主,侧重讨论计算机硬件系统的运算器、控制器、存储器等部件的工作原理、相互关系以及分析、设计方法。通过课程的学习,要求学生掌握计算机硬件系统主要组成部件的工作原理和分析设计方法,具备对相关硬件系统进行分析和设计的能力。实验教学在本课程的教学中具有非常重要的作用。教改前与教改后的实验都涵盖了运算器设计、存储器设计和CPU设计三方面的内容,实验课时都是8学时。

教改前,软件工程、信息安全等专业要求学生使用FPGA来完成实验,但由于这些专业没有开设电路分析、模拟电子和EDA等先修课程,学生没有硬件描述语言编程方面的知识基础,大部分学生不具备独立完成实验的能力,最终导致设计性实验变成了验证性实验。学生只是阅读代码、下载运行、查看结果,学生的计算机硬件系统的设计能力并没有得到有效训练,教学效果和教学目标达成情况不理想。