集成电路中的噪声抑制与信号完整性保障技术研究

作者: 张凯棋

摘要:文章聚焦于集成电路中的单点接地技术在噪声抑制与信号完整性保障方面的应用。详细阐述了从确定公共接地点、连接电路元件到公共接地点以及检查接地回路的流程,分析了单点接地技术在抑制噪声和保障信号完整性方面的有效性。实验结果表明,采用该技术后,信号的上升时间和下降时间明显缩短,信号更加平滑地传输,信号完整性得到提高,可以为集成电路设计提供针对性的技术指导。

关键词:集成电路;噪声抑制;信号完整性;保障技术

中图分类号:TU71 文献标识码:A

文章编号:1009-3044(2025)06-0123-03 开放科学(资源服务)标识码(OSID)

0 引言

在当今高度集成化的电子时代,集成电路宛如电子设备的心脏,在智能手机、计算机、智能家电以及航空航天等各类领域的电子设备中都发挥着无可替代的核心作用[1]。集成电路的高效运行是确保设备正常工作以及实现复杂功能的关键。然而,集成电路在运行过程中面临着一个严峻的挑战——噪声干扰。这些噪声犹如潜伏在电路中的隐形敌人,严重影响了信号的完整性,且噪声来源多样,部分源于物理机制[2-3]。

噪声可能源于热运动、粒子的离散性等物理机制,这些机制会导致信号出现失真、延迟以及不同信号间的串扰等不良影响。这些问题不仅降低了集成电路的性能,甚至可能导致整个系统的故障。保障技术,是指为确保特定系统(如军事装备系统、信息网络系统等)稳定、可靠运行,在预防故障、快速检测故障、有效修复故障以及维持系统性能等方面所采用的一系列技术手段。

因此,本文研究了集成电路中的噪声抑制与信号完整性保障技术。通过采取单点接地技术措施来抑制噪声和保障信号完整性,极大地提高了集成电路的质量与可靠性,满足了现代电子设备对高性能和高稳定性的需求。

1集成电路中的单点接地技术要点

确定合理的公共接地点可以有效避免不同接地点之间形成地环路。地环路会在其中产生电流,由于周围磁场变化等因素而引入噪声[4-5]。而单点接地(通过确定公共接地点实现)可有效破坏地环路形成的条件,降低噪声对集成电路的影响,保障信号完整性。

1.1确定公共接地点

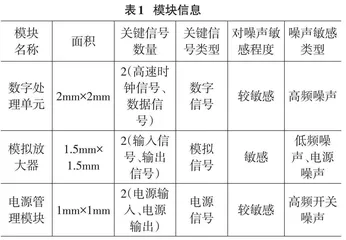

观察集成电路版图并划分功能模块,如数字模块、模拟模块、电源模块等。假设一个集成电路中包含一个数字处理单元(面积约为2mm×2mm)、一个模拟放大器(面积约为1.5mm×1.5mm)和一个电源管理模块(面积约为1mm×1mm),统计每个模块中关键信号的数量和类型,以及对噪声的敏感程度,如表1 所示。

数字处理单元中有高速时钟信号和数据信号,对高频噪声较敏感;模拟放大器对低频噪声和电源噪声敏感,通过对电路模块的划分和对各模块信号及噪声特性的分析,能够明确整个集成电路中噪声产生和敏感的区域分布,为选择合适的公共接地点提供依据。确定主要信号的传输路径,从信号源到信号接收端。

沿着信号流向,标记出可能产生噪声的区域和对噪声敏感的区域,模拟放大器和数字处理单元之间的接口区域因为信号转换而产生噪声,而模拟放大器的输入级对噪声最为敏感。根据前面分析的电路模块分布和信号流向,找到一个相对处于各个模块几何中心的位置。假设数字处理单元中心坐标为(10mm,10mm),模拟放大器中心坐标为(8mm,8mm),电源管理模块中心坐标为(6mm,6mm),则公共接地点的初步坐标可以选择为(8mm,8mm)左右。用几何中心坐标公式,假设集成电路中有n 个模块,第i 个模块的中心坐标为(x ) i,yi ,则公共接地点的初步X 坐标如式(1)所示:

通过这个公式可以快速计算出一个大致的中心位置,作为选择公共接地点的参考。在上述例子中,根据公式计算出的初步位置能够使公共接地点在空间上相对均衡地分布在各个电路模块之间,减少了某些模块因为距离接地点过远而导致的地电位升高和噪声耦合问题。

同时,要考虑这个位置周围的干扰情况。避免选择靠近高频时钟信号走线、大电流电源走线或者其他强干扰源的位置。如果在初步选定的位置附近(半径1mm范围内)存在一条宽度为0.5mm的高频时钟走线(时钟频率为500MHz),则需要将公共接地点位置稍微偏移,远离这条走线,用距离公式,设两个点的坐标分别为(x1,y1)和(x2,y2),则两点之间的距离d如式(3)所示:

在确定公共接地点位置时,如果发现初步选定的位置附近存在干扰源(如高频走线等),可以使用这个公式计算干扰源与初步选定位置之间的距离。当计算出初步位置与高频时钟走线的距离小于一定阈值(如1mm)时,可以判断该位置可能受到较大干扰,需要进行调整。

1.2连接电路元件到公共接地点

对于一般的集成电路,通常选择宽度为0.2mm~0.5mm的金属走线作为接地导线,这是基于常见集成电路制造工艺中,该宽度的金属走线在一定长度范围内能提供相对较低的阻抗。对于关键的低噪声元件,如高精度模拟放大器的输入级,需要优先连接到公共接地点,低噪声放大器的具体连接情况,如图1所示。

低噪声放大器(LNA)的连接结构主要包括两个部分:输出匹配网络和输入匹配网络,它们分别连接到放大器的两端。输出匹配网络位于图像左侧,与放大器相连,其功能是确保信号能够有效地从放大器传输到外部设备或电路中。输入匹配网络位于图像右侧,同样与放大器相连,确保信号能够从外部设备或电路有效地传输到放大器中。

放大器是整个结构的中心部分,负责接收来自输入匹配网络的信号,放大该信号,并将其通过输出匹配网络传输出去,以增强信号的功率。假设该放大器的输入级距离公共接地点的直线距离为1mm,使用0.3mm宽的金属走线进行连接。在连接过程中,需确保其他大电流元件的接地导线与关键元件的接地路径不交叉。具体来说,一个大电流数字模块的接地导线与高精度模拟放大器输入级的接地导线之间应保持至少0.5mm的距离(根据经验和设计规范)。

使用专业的电路检测工具,对每个元件的接地连接进行电阻测试。要求每个接地连接的电阻值小于0.1Ω,通过测试确保所有元件的接地连接都满足此要求。

1.3检查接地回路

使用HSPICE 软件对单点接地集成电路进行仿真,在软件中设置好电路的各个元件参数、接地方式以及信号源等相关参数,设定信号源为一个频率从10kHz~100MHz变化的正弦波信号,幅度为1V,负载电阻为100Ω,接地导线电阻根据前面步骤计算出的值(假设为0.05Ω)进行设置。

在仿真软件中查看接地电流的分布情况以及各个节点的电位,重点关注是否存在意外的接地环路。如果在某个频率(如50MHz)下,发现有两个接地路径之间形成了一个面积约为0.1mm²的闭环电流路径,这可能就是一个潜在的接地环路问题。当发现潜在接地环路时,使用公式(4)来计算接地环路电感L:

式中,μ0 = 4π × 10-7H/m 是真空磁导率,μr 是相对磁导率(对于集成电路中的常见材料,假设μr=1),A是接地环路面积(如前面发现的0.1mm²,换算为1 ×10-7m2),l 是接地环路的平均周长(假设通过测量或估算为1mm,即0.001m)。计算出接地环路电感后,可以评估其对高频信号的影响,电感较大可能导致在高频下产生较大的感应电压,从而引入噪声。根据接地环路的情况和计算出的电感值,如果电感值较大则需要重新调整元件布局或者接地连接方式。将形成接地环路的两个元件之间的距离增大,从原来的0.5mm增大到1.5mm,或者改变接地导线的连接路径,避免形成闭环。

在集成电路版图设计完成后进行物理验证,使用专业的Calibre物理验证工具检查接地连接是否符合设计要求,是否存在潜在的短路或者开路情况,从而抑制集成电路中的噪声。

2信号完整性测试实验

2.1实验准备

假设在一个高速数字通信集成电路的研发过程中,需要对信号完整性进行测试。该集成电路用于数据中心的高速数据传输,传输速率高达10 Gbps。在系统硬件设备设计中,信号发生器型号为Agilent81160A,能够产生高精度、高频率的测试信号,频率范围为10 MHz至12.75 GHz。Tektronix DPO73304DX示波器具有33 GHz的带宽和100 GS/s的采样率,可以精确捕捉高速信号的波形。实验专门设计了测试电路板,包含待测试的集成电路以及相关的外围电路,如电源电路、时钟电路等。电路板采用多层PCB设计,以模拟实际应用中的布线环境。

Keysight E5071C阻抗分析仪用于测量传输线的阻抗特性,频率范围为5 Hz至20 GHz。将信号发生器通过高质量的同轴电缆连接到测试电路板的信号输入端,确保连接牢固,以减少信号反射和损耗。用另一根同轴电缆将测试电路板的信号输出端连接到示波器的输入通道,同时将阻抗分析仪通过测试探头连接到测试电路板上的传输线,用于测量阻抗。

2.2实验结果

在信号发生器上设置输出信号的频率为(或改为“相当于”)10 Gbps的速率(注:此处原文直接设置频率为10Gbps不准确,因为频率通常指信号变化的快慢,而Gbps是数据传输速率,但为保持原文意图,这里做了说明性修改),信号幅度为1 Vpp(峰-峰电压),信号类型为伪随机二进制序列(PRBS),以便模拟实际的数据信号。配置示波器的触发模式为边沿触发,触发源为测试信号通道,触发电平设置为信号幅度的50%。同时,设置示波器的采样率为80 GS/s,以确保能够准确捕获信号的细节。

阻抗分析仪设置为扫频模式,频率范围从1 MHz 至10 GHz,以测量不同频率下传输线的阻抗特性。检查测试电路板上的集成电路是否焊接良好,确保所有引脚与电路板的连接无短路和开路现象。对电路板进行预热,将环境温度稳定在25°C ± 1°C,以消除温度对测试结果的影响。应用后的实验结果如表2所示。

由表2可知,采用保障技术后,信号的上升时间和下降时间都明显缩短。这意味着信号在传输过程中的转换速度更快,减少了信号在不同状态之间的过渡时间,从而降低了信号受到噪声干扰的可能性。信号过冲从15%降低到5%,说明信号的稳定性得到了显著提高。过冲可能导致信号超出电路元件的承受范围,引起信号失真甚至损坏元件。降低过冲可以使信号更加平滑地传输,提高信号完整性,信号眼图张开度从200mV增加到350mV,表明信号的质量得到了改善。

信号眼图张开度越大,说明信号在传输过程中的抗干扰能力越强,信号的误码率越低。在5GHz时,传输线阻抗更接近设计目标值(假设设计目标阻抗为50Ω)。阻抗匹配对于信号完整性至关重要,匹配的阻抗可以减少信号反射,提高信号传输效率。

3结束语

综上所述,单点接地技术在集成电路的噪声抑制与信号完整性保障中发挥着关键作用。从确定公共接地点的位置,到将电路元件合理连接到公共接地点,再到仔细检查接地回路,每一个步骤都对最终的效果产生重要影响。通过优化这些环节,可以有效降低集成电路中的噪声,保障信号的完整性。随着集成电路技术的不断发展,单点接地技术仍有进一步优化的空间。未来的研究可以在现有基础上,进一步探索公共接地点的精确确定方法、连接方式的改进措施以及接地回路检查方法的完善途径,以更好地适应集成电路设计的需求,推动集成电路向高性能和高可靠性方向发展。